# **HP-CAST 12**

# ESTABLISHED IN 1993 IN SANTIAGO DE COMPOSTELA (SPAIN)

**To provide** high performance computing and communication resources and services to the scientific community of Galicia and to the National Research Council (CSIC), as well as, to institutions and enterprises with R&D activity.

**To promote** the use of new information and communication technologies applied to research within the scientific community of Galicia.

- Galician Universities

- Galician Regional Government Research Centres

- Spanish National Research Council (CSIC) Centres

- Other public or private organizations worldwide

- Hospital R&D Departments

- Industries R&D Departments

- Technological & Research Centres

- Other Universities worldwide

- Non-profit R&D organizations

- HPC, HTC & GRID Computing

- User Data Storage

- Advanced Communications Network

- e-Learning & Collaboration Infrastructures

- GIS (Geographical Information Systems)

- Transfer to the industry and e-Business Innovation

Support

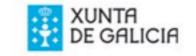

#### **New HPC Supercomputer 2007**

More than: 16,000 GFLOPS 2,580 CPUs 19,000 GB Memory

InfiniBand network SuSE Linux

Ranked 100<sup>th</sup> in the Top500 list of November 2007

#### Finis Terrae (2007)

#### **Supercomputing Nodes:**

147 cc-NUMA Nodes with Itanium CPUs connected through a high performance InfiniBand network (20 Gbps)

☑ 1 node: 128 cores, 1024 GB memory

■ 2 nodes: 64 cores, 128+256 GB memory

■ 142 nodes: 16 cores, 128 GB memory

■ 2 testing nodes: 4 cores, 4 GB memory

#### **Parallel Filesystem HP-SFS:**

- ☑ 20 Nodes (2x Dual-core Intel Xeon 5160 CPUs)

- **図 864 Hard Disks**

- **図 210 TB**

- **Based on Lustre** ■

- ☑ Accessed through the InfiniBand network

#### Finis Terrae (2007)

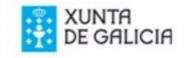

**Source: Intel**

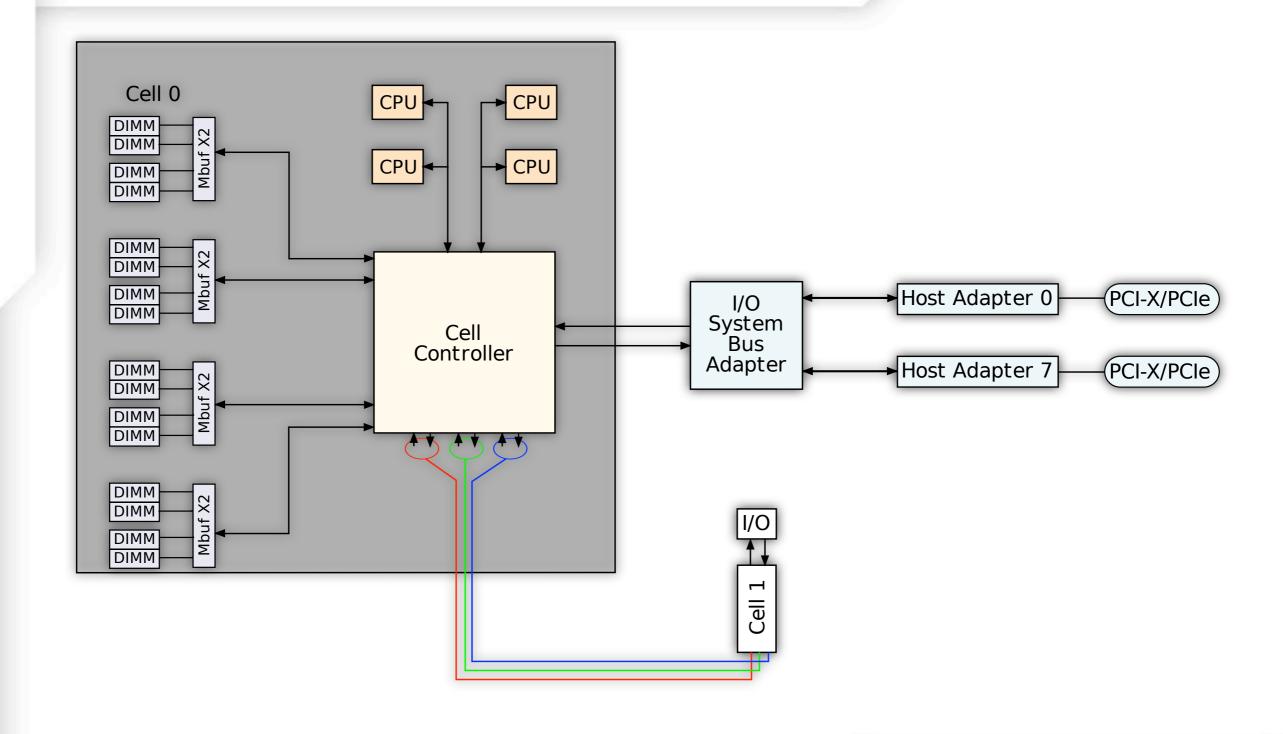

# **HP Integrity RX 7640:**

- 16 Cores

- 2 Cells

- 1 InfiniBand HCA

#### **HP Integrity RX 7640:**

- 16 Cores

- 2 Cells

- 1 InfiniBand HCA

- It is not only a bottleneck (it is placed on one cell, what about the other one?)

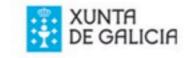

- In Nehalem/Opteron machines the problem is quite similar (there is no cells, but they are NUMA machines with I/O interfaces associated to one/two processors)

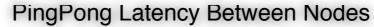

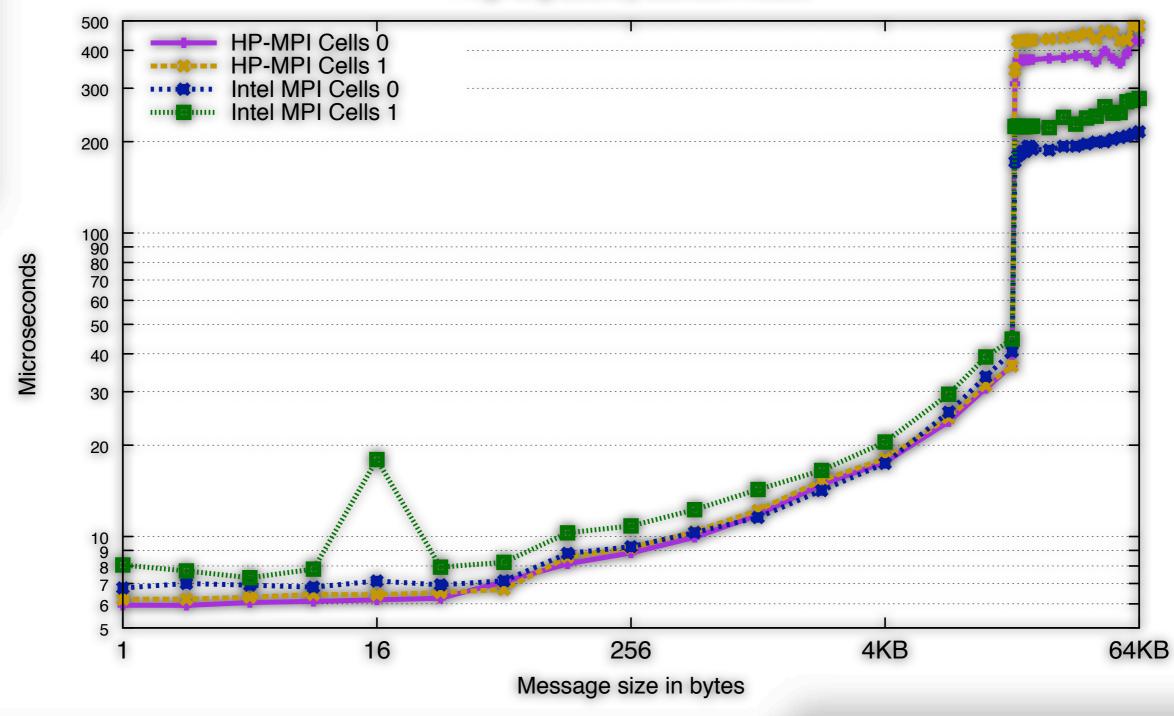

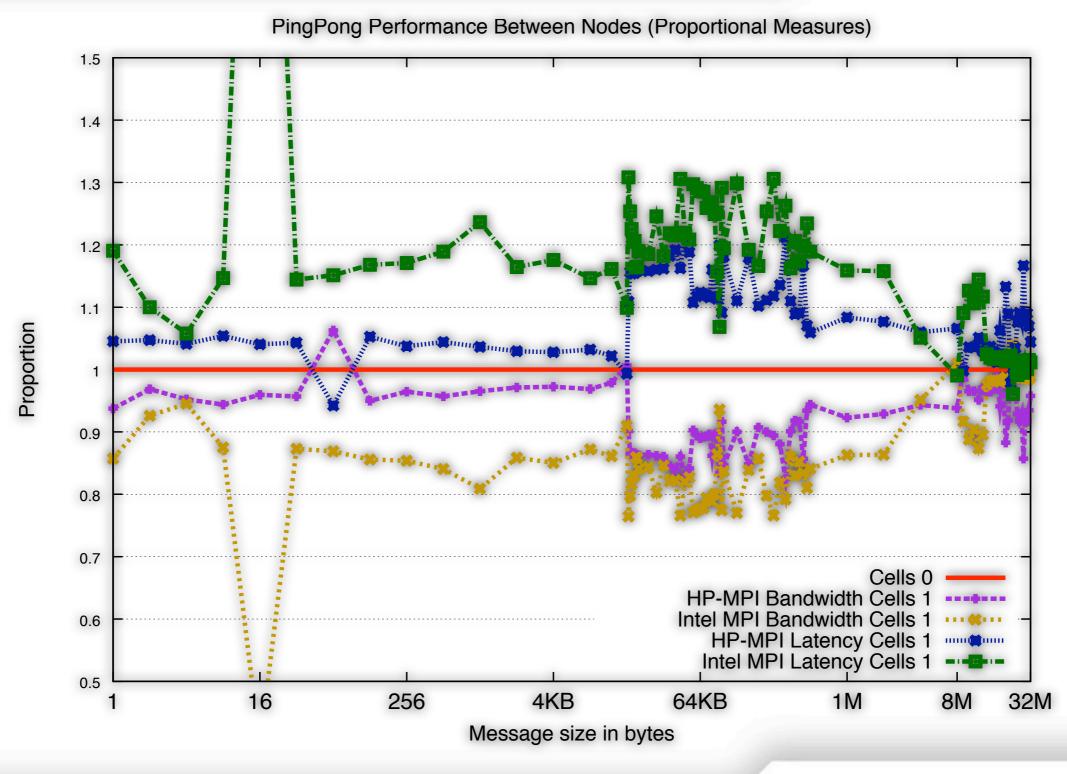

### **Point to point:**

- Roughly 20% in average

- Up to 30%

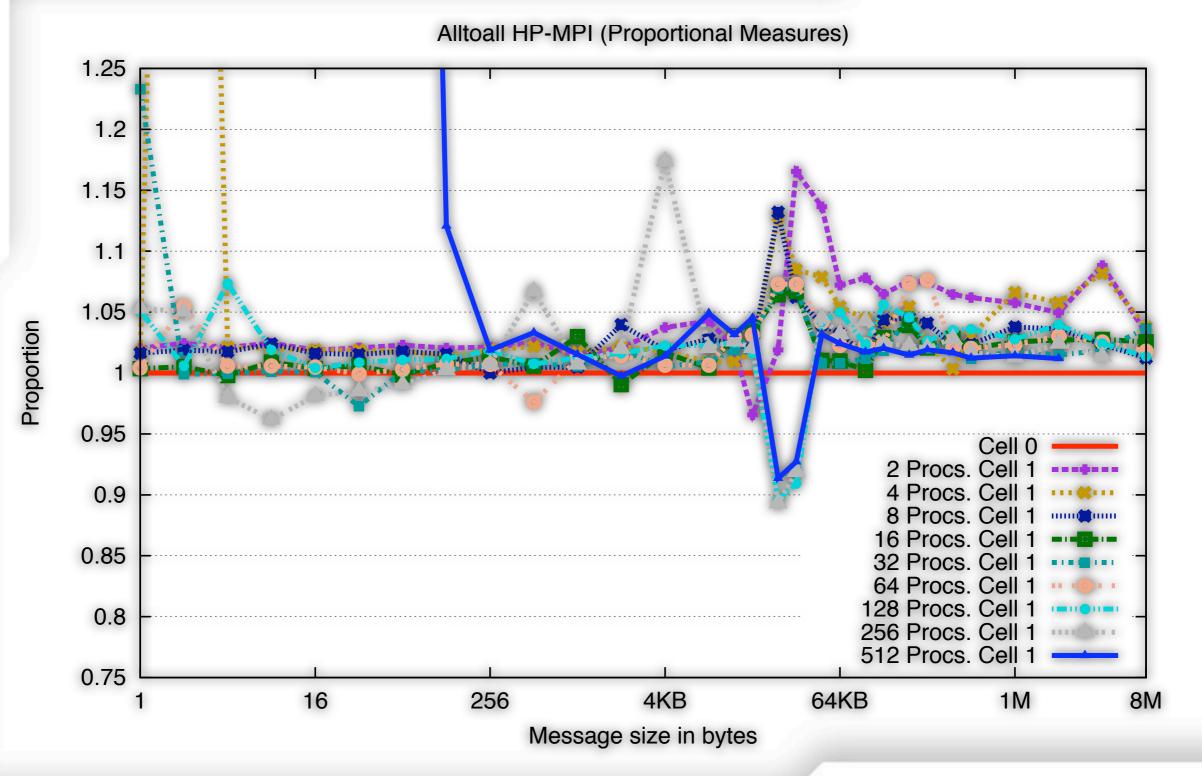

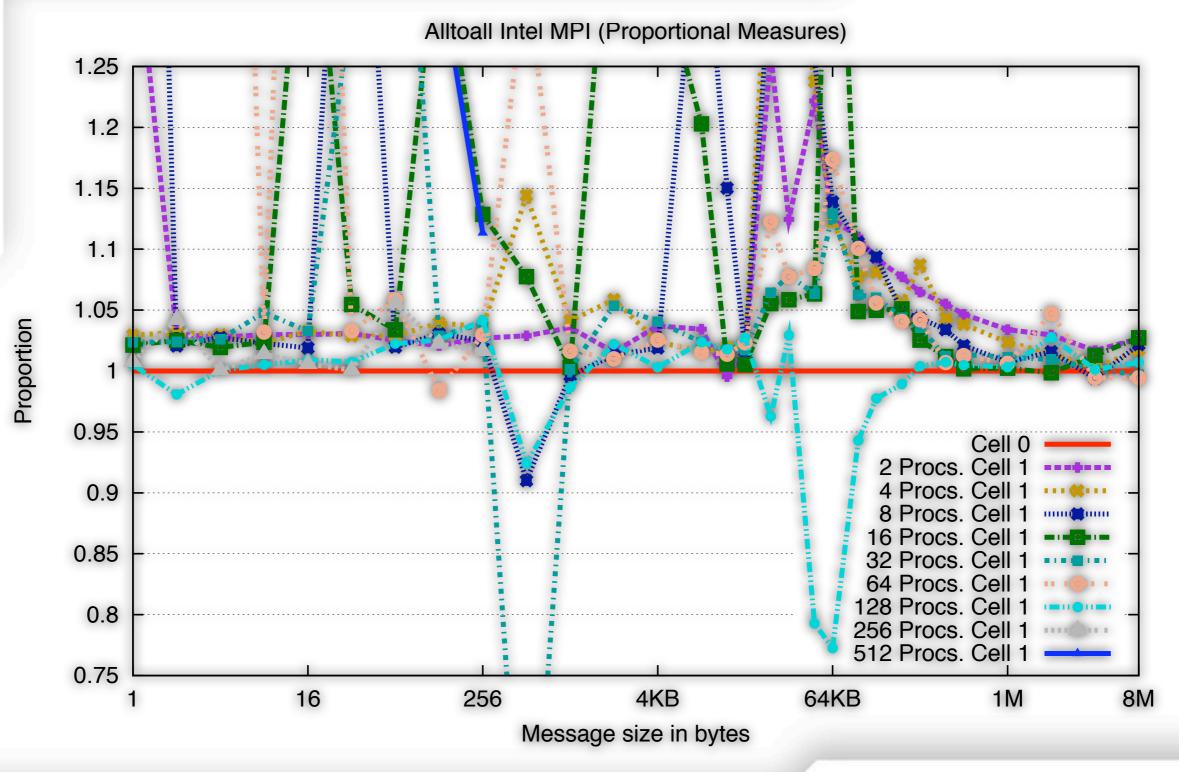

### Collectives (All to all):

- Roughly 3% in average

- Up to 15% (With HP-MPI. With Intel MPI unstable -but consistent- measures)

### **Systems made of:**

- 64? (RX-like) 512? (Superdome-like) cores

- 2? 16? cells

- 1 InfiniBand HCA?

- How would it perform in a MPI\_Alltoall operation?

- **⊙** The scenario is quite similar in the x86-64 world.

### **Current setups:**

- Noticiable differences (not HUGE, but noticeable)

- Collective operations are less affected

- The time spended due to the algorithm complexity and intranode communications hides the problem

- Users can benefit from carefully planned affinity (specially SFS users)

### **Future setups:**

- The problem might become:

- Bigger (more cores accessing non-local HCA or an HCA accessing more non-local data -RDMA-)

- Widespreaded (all x86-64 systems will be NUMA)

#### **Solution:**

- Add hardware (HCAs)

- **⊙** But it is expensive. Does it compensate?

- And we/runtime/application can not choose the HCA to be used

- What do we do now?

#### **Solution:**

- Add hardware (HCAs)

- But it is expensive. Does it compensate?

- And we/runtime/application can not choose the HCA to be used

- What do we do now?

- It is necessary to develop some mechanisms to allow the software stack (driver "routing"?) to choose the "nearest" HCA

# Thank you!

dalvarez@cesga.es